# ARENBERG DOCTORAL SCHOOL Faculty of Engineering Science

# Interface Sanitization and Real-Time Scheduling for Enclaved Execution

# Fritz Alder

Supervisors:

Prof. dr. ir. F. Piessens

Prof. dr. J.T. Mühlberg

Dr. ir. J. Van Bulck

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Computer Science

# Interface Sanitization and Real-Time Scheduling for Enclaved Execution

## Fritz ALDER

Examination committee:

Prof. dr. ir. H. Neuckermans, chair

Prof. dr. ir. F. Piessens, supervisor

Prof. dr. J.T. Mühlberg, supervisor

Dr. ir. J. Van Bulck, supervisor

Prof. dr. ir. W. Joosen

Prof. dr. N. Smart

Prof. dr. D. Oswald

(University of Birmingham)

Prof. dr. S. Shinde

(ETH Zurich)

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Computer Science © 2023 KU Leuven – Faculty of Engineering Science Uitgegeven in eigen beheer, Fritz Alder, Celestijnenlaan 200A box 2402, B-3001 Leuven (Belgium) Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt worden door middel van druk, fotokopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever. All rights reserved. No part of the publication may be reproduced in any form by print, photoprint, microfilm, electronic or any other means without written permission from the publisher.

# **Preface**

Writing this preface is both a daunting and exciting conclusion of my four years at KU Leuven. Exciting, because I have been looking forward to doing research and a Ph.D. since starting my master's and since I delved ever deeper into the fascinating rabbit hole of cyber security. A global pandemic roughly six months after I moved to Belgium did not make it easy for me and many others but it at least never deterred me from wanting to do more research. At the same time, writing this preface is daunting because throughout my career I have been surrounded by great, compassionate, and truly intelligent people. Trying to name all of you who have impacted me directly or indirectly, or have helped me along the way is nearly impossible. But I shall try.

First and foremost, I wish to thank my supervisor Frank Piessens, for being simply the best supervisor I could have wished for. It is rare to see a supervisor who not only gives his students full freedom with no questions asked but also manages to always be available and responsive when needed. And somehow you manage to do it while always giving meaningful insights. You keep saying advice is worth what you pay for it and I feel that my debt to you must be immense by now. Sincerely thank you.

I next want to thank Jan Tobias Mühlberg. Not only did you immediately take me in after I sheepishly asked whether there were open positions, but you also gave me the freedom to go fully astray from what we originally planned for this dissertation.

The last person on my supervisory committee is Jo Van Bulck, who partly was the reason for my diversions of the original research trajectory. Thank you for too many things to count here. I really enjoyed working with you for these years and loved our little hack sessions, extended design discussions, disagreements, and late-night conference discussions.

I wish to thank the external as well as the local members of my Ph.D. jury: Herman Neuckermans, Wouter Joosen, Nigel Smart, David Oswald, and Shweta

i

ii \_\_\_\_\_\_PREFACE

Shinde. I feel honored to have had all of you on my jury and truly enjoyed our interactions throughout the process. I especially wish to thank David for the years of fruitful and fun collaboration.

Outside of my jury, I first wish to thank my direct collaborators Gianluca Scopelliti, Lesly-Ann Daniel, Jan Pennekamp, Roman Matzutt, Christoph Baumann, and Sepideh Pouyanrad. I thoroughly enjoyed working with you. I am especially happy that Gianluca decided to still work with me after doing his master's thesis with me.

Next, I want to thank my colleagues and friends in and around DistriNet: Job Noorman, Hans Winderix, Márton Bognár, Vera and Snezhok Rimmer, Merve Turhan, Gilang Hamidy, Antoon Purnal, Gerald Budigiri, Tobias Reinhard, Annick Vandijck, An Makowski, Katrien Janssens, and all the other friendly faces that made the office a nice place to be at.

Outside of KU Leuven, I want to thank the people in and around the Secure Systems Group in Finland. Thank you, Asokan and Andrew Paverd, for still taking me into your group after I initially (stupidly) refused your offer, and thank you for the best start I could have wished for in my research career. Thank you also to Ilhan Gurel, Thomas Nyman, Sebastian Szyller, and Koen Tange. Thank you, Lukas Prediger, for the (almost) weekly chats, and thank you to the other members of Group One for persistently being a great exchange family. I also wish to thank Stefan and Christian Teutrine, as well as Anika Werner. Also thank you, Finn, for bringing everyone some joy.

Coming to a close, I wish to thank my family and most importantly, my parents. Love needs constant care and reassessment. And you two have so much of it, you keep radiating that love to everyone you meet. That I keep moving around in the world and you by now know time zones and flight tracker websites by heart is a result of your success as parents, not your fault – I promise! Being so far away so often (and at the worst times) meant that I saw my older brother Florian only a fraction of what I would have wished for these past years. Still, I am immensely grateful to have grown up with you and for the bond we share. Ich bin stolz auf euch drei.

Last, I thank my partner Sonja for so many things. I am continuously amazed and happy to have found you. Thank you for always being there for me and suffering through hundreds of iterations of my slide graphics and endless excited descriptions of weird security topics. I look forward to wherever the road leads us.

— Fritz Alder October 2023, Leuven PREFACE \_\_\_\_\_\_ ii

This work was supported by a Ph.D. Fellowship from the Research Foundation — Flanders (FWO) and by the Research Fund KU Leuven.

# **Abstract**

Modern computing is increasingly characterized by an abundance of connectivity between networked devices and a sharing of resources on local devices. While this development has created a range of positive opportunities in terms of productivity and technical capabilities, it also opens up modern systems to security issues that were not as critical in the previously insulated systems. Protecting confidentiality and integrity has thus become an integral concern and isolation mechanisms already enabled a type of computing where programs share their resources with other, entirely untrusted, programs.

One approach to ensure the security on such systems are hardware isolation approaches, such as trusted execution environments (TEEs). TEEs aim to isolate programs and shield them from accesses by any other part of the system that is not within the trusted computing base. Specifically, hardware-based TEEs achieve this by employing modifications to the underlying computing architecture that limit access to specific interactions and deny any other access. One type of TEE protects code in so-called *enclaves* that draw the protection boundary at the program level and usually require coordinated interactions between an untrusted and a trusted program within the same address space.

This dissertation advances the state of the art for this type of TEEs in two directions. First, we investigate availability guarantees on lightweight architectures and equip TEEs for real-time applications. We do this with a hardware-software co-design that places a real-time scheduler inside of an enclave, in order to provide other enclaves with strong availability guarantees. This allows us to combine the approach of openly sharing resources between mutually distrusting parties with the realm of safety-critical devices that must meet real-time deadlines. Our solution can be seen as a first step to apply modern TEE capabilities to the slow-moving but critical area of real-time and mixed-criticality systems on lightweight computing architectures.

vi \_\_\_\_\_\_ ABSTRACT

Second, this dissertation investigates software responsibilities of Intel Software Guard Extensions (SGX) enclave shielding runtimes. This growing and diverse ecosystem is not sufficiently understood and we make contributions in two parts. First, we manually find and report issues at the low-level transition between enclave and untrusted domain. Our work shows that every extended architectural feature in a processor that the enclave may rely on must be adequately sanitized and initialized to a secure state before being used inside the isolated area. The results show that low-level configuration registers for floatingpoint accelerators are widely overlooked, and the impacts of this misconfiguration are more dangerous than may be intuitive. Since modern processor architectures are increasingly complex and legacy features are rarely removed, we then develop a tool that helps in automatically finding interface vulnerabilities. This tool, named Pandora, targets the crucial area of enclave shielding runtimes that provide the basis for most projects running in enclave-based TEEs like Intel SGX. Pandora saves the enclave memory at creation time and then uses symbolic execution to simulate execution of this truthful view of the enclave. We use Pandora to automatically detect multiple vulnerabilities across various enclave shielding runtimes, and use it to help vendors in validating their applied mitigations. Our work on Pandora is the first analysis of arbitrary Intel SGX enclaves that is able to automatically find vulnerabilities such as the vulnerability class of improper pointer alignment.

In summary, this dissertation extends the range of applicability of TEEs and secures TEEs by uncovering new vulnerabilities and automatically finding known vulnerabilities in enclave software. Our work thus serves as a fundament for future work to strengthen the capabilities of future TEEs and helps projects to secure their software on existing TEEs against known vulnerabilities.

# **Beknopte Samenvatting**

Het gebruik van moderne informatietechnologie leidt tot meer productiviteit en technische mogelijkheden, zowel door de toenemende connectiviteit in computernetwerken, als door het delen van computersystemen door meerdere, onderling onvertrouwde applicaties. Deze evoluties stellen hedendaagse computersystemen echter ook in toenemende mate bloot aan beveiligingsproblemen en onderstrepen het belang van het beschermen van vertrouwelijke informatie en integriteit van berekeningen.

Een belangrijke bouwsteen om de veiligheid van computersystemen te garanderen, is hardwarematige isolatie, waar recente ontwikkelingen op het gebied van vertrouwde uitvoeringsomgevingen bijzonder veelbelovend lijken. Zulke vertrouwde uitvoeringsomgevingen stellen aanpassingen voor aan de onderliggende computerarchitectuur om beschermde programma's strikt af te schermen in zogenaamde *enclaves*, die geïsoleerd zijn van alle andere, onvertrouwde software op het doelapparaat, inclusief zelfs het besturingssysteem.

Dit proefschrift draagt bij aan het verbeteren van hedendaagse vertrouwde uitvoeringsomgevingen op twee manieren. Ten eerste richten we ons op kleine, ingebedde computerchips en onderzoeken we hoe vertrouwde uitvoeringsomgevingen kunnen ingezet worden in real-time omgevingen. Ons resulterende hardware-software co-design zondert een real-time planningsalgoritme af in een bevoorrechte enclave, om zo de beschikbaarheid van afzonderlijke applicatieenclaves te garanderen. Deze oplossing vormt een eerste stap om vertrouwde uitvoeringsomgevingen uit te breiden met sterke beschikbaarheidsgaranties, zodat dat ze kunnen worden ingezet voor het beveiligen van kritische, ingebedde apparaten die strikte real-time deadlines moeten halen.

Ten tweede onderzoeken we de resterende softwareverantwoordelijkheden voor enclaves die gebruik maken van de wijdverspreide SGX-extensies in recente Intelprocessoren. Dit proefschrift bevordert de veiligheid van het groeiende en diverse SGX-ecosysteem op twee manieren. Als eerste bijdrage ontdekken en rapporteren

we subtiele gebreken in de cruciale initialisatielogica die verantwoordelijk is om de overgang naar de enclave in goede banen te leiden. Meer bepaald laat onze studie van populaire SGX-ontwikkelingsomgevingen zien dat het veilig initialiseren van processorconfiguratieregisters voor zwevendekommabewerkingen op grote schaal over het hoofd werd gezien. In verschillende praktische aanvalsscenario's tonen we bovendien aan dat de gevolgen van deze verkeerde configuratie gevaarlijker zijn dan intuïtief kan lijken. Dit vormt de motivatie voor onze tweede bijdrage, waar we een automatische methode onderzoeken om interfacekwetsbaarheden in SGX-ontwikkelingsomgevingen te vinden. Daarbij ontwikkelen we een praktische toepassing, Pandora genaamd, die het geheugen van een willekeurige SGX-enclave waarheidsgetrouw kan reconstrueren om vervolgens een symbolische uitvoering van de enclave nauwgezet te simuleren. Pandora is in staat om automatisch meerdere onbekende kwetsbaarheden te detecteren in verschillende SGX-ontwikkelingsomgevingen en kan bovendien helpen om de toegepaste mitigaties te valideren.

Samengevat breidt dit proefschrift het toepassingsgebied van vertrouwde uitvoeringsomgevingen uit naar real-time omgevingen, en dragen we bij aan het beter begrijpen en valideren van resterende softwareverantwoordelijkheden. Ons werk kan dus als basis dienen voor toekomstig onderzoek om de mogelijkheden en veiligheid van opkomende vertrouwde uitvoeringsomgevingen te versterken, zowel op hardware als op software vlak.

# **Contents**

| ΑI | ostra | ct                                            | V     |

|----|-------|-----------------------------------------------|-------|

| В  | eknop | ote Samenvatting                              | vii   |

| C  | onten | nts                                           | ix    |

| Li | st of | Figures                                       | xiii  |

| Li | st of | Tables                                        | χV    |

| Li | st of | Abbreviations                                 | xviii |

| 1  | Intr  | oduction                                      | 1     |

|    | 1.1   | Confidential Computing                        | 2     |

|    |       | 1.1.1 Enclave Architectures                   | 5     |

|    |       | 1.1.2 Sancus                                  | 6     |

|    |       | 1.1.3 Intel SGX                               | 7     |

|    | 1.2   | Dissertation Motivation and Contributions     | 10    |

|    |       | 1.2.1 Availability Guarantees for Enclaves    | 10    |

|    |       | 1.2.2 Interface Sanitization in Intel SGX     | 11    |

|    |       | 1.2.3 Open Science and Ethical Considerations | 13    |

|    | 1.3   | Other Contributions                           | 14    |

|    | 1.4   | Dissertation Outline                          | 17    |

| 2  | Aic   |                                               |       |

|    | Gua   | arantees for Enclaves                         | 19    |

|    | 2.1   |                                               | 21    |

|    | 2.2   |                                               | 23    |

|    |       | 2.2.1 Generalized Base Platform               | 23    |

|    |       | 2.2.2 A Running Example                       | 25    |

|    |       | 2.2.3 Security & Availability Guarantees      | 26    |

x \_\_\_\_\_CONTENTS

|   | 2.3 | Design                                                     | 28  |

|---|-----|------------------------------------------------------------|-----|

|   |     | 2.3.1 TEE Architecture                                     | 29  |

|   |     | 2.3.2 Exception Engine                                     | 30  |

|   |     | 2.3.3 Atomicity Monitor                                    | 33  |

|   |     | 2.3.4 Enclaved Scheduler                                   | 35  |

|   | 2.4 | Prototype Implementation                                   | 36  |

|   |     | 2.4.1 Background: Sancus and RIOT                          | 36  |

|   |     | 2.4.2 Modifications to Sancus                              | 38  |

|   |     | 2.4.3 Modifications to RIOT                                | 40  |

|   | 2.5 | Experimental Evaluation                                    | 41  |

|   | _   | 2.5.1 Case Study                                           | 41  |

|   |     | 2.5.2 Performance Evaluation                               | 43  |

|   | 2.6 | Discussion and Security Analysis                           | 46  |

|   | 2.7 | Conclusion                                                 | 49  |

|   |     |                                                            | 10  |

| 3 | Fau | Ity Point Unit: ABI Poisoning Attacks on Trusted Execution |     |

|   | Env | ironments                                                  | 51  |

|   | 3.1 | Introduction                                               | 54  |

|   | 3.2 | Background                                                 | 59  |

|   |     | 3.2.1 Intel SGX                                            | 59  |

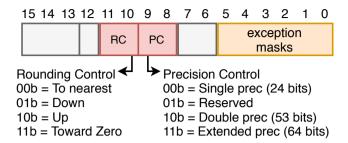

|   |     | 3.2.2 x87 FPU                                              | 59  |

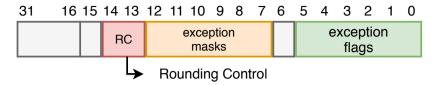

|   |     | 3.2.3 Streaming SIMD Extensions (SSE)                      | 61  |

|   |     | 3.2.4 Other Processor Architectures                        | 63  |

|   | 3.3 | Poisoning FPU State Registers                              | 64  |

|   |     | 3.3.1 Attacker and System Model                            | 64  |

|   |     | 3.3.2 ABI Poisoning Attacks                                | 65  |

|   |     | 3.3.3 TEE Runtime Vulnerability Assessment                 | 70  |

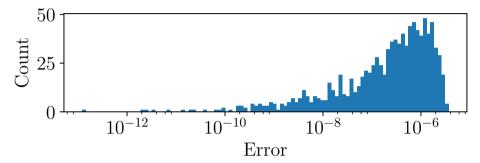

|   | 3.4 | Case Study: Floating-point Exceptions as a Side Channel    | 73  |

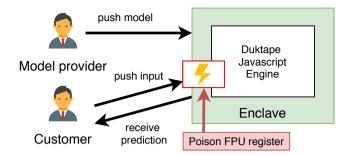

|   | 3.5 | Case Study: Attacking Machine Learning Predictions         | 78  |

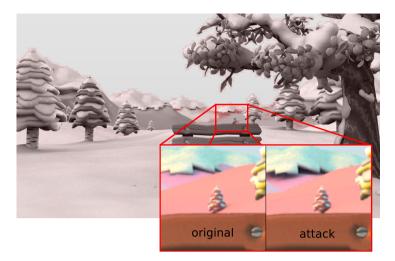

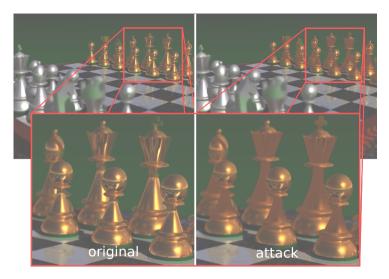

|   | 3.6 | Case Study: Spec Benchmarks                                | 82  |

|   | 3.7 | Conclusions and Lessons Learned                            | 86  |

|   |     |                                                            |     |

| 4 |     | dora: Principled Symbolic Execution of Intel SGX Enclaves  | 89  |

|   | 4.1 | Introduction                                               | 91  |

|   | 4.2 | Background and Related Work                                | 93  |

|   | 4.3 | Problem Statement and Overview                             | 96  |

|   |     | 4.3.1 Research Gap                                         | 96  |

|   |     | 4.3.2 Solution Overview                                    | 98  |

|   | 4.4 | Enclave-Aware Symbolic Execution $(G1)$                    | 100 |

|   |     | 4.4.1 Modeling x86 Instruction Semantics                   | 100 |

|   |     | 4.4.2 Taint Tracking of Attacker Inputs                    | 100 |

|   |     | 4.4.3 Enclave-Aware Memory Model                           | 101 |

|   |     | 4.4.4 Enclave Entry and Reentry                            | 103 |

CONTENTS \_\_\_\_\_\_xi

|     |        | 4.4.5 Path Exploration and State Reduction                 | 103 |

|-----|--------|------------------------------------------------------------|-----|

|     | 4.5    | Runtime-Agnostic Enclave Loading $(G2)$                    | 104 |

|     | 4.6    | Pluggable Vulnerability Detection $(G3)$                   | 106 |

|     |        | 4.6.1 ABI-Level CPU Register Sanitization                  | 107 |

|     |        | 4.6.2 Untrusted Pointer Value Sanitization                 | 109 |

|     |        | 4.6.3 Untrusted Pointer Alignment Sanitization             | 110 |

|     |        | 4.6.4 Control-Flow Hijacking Validation                    | 111 |

|     | 4.7    | Evaluation                                                 | 112 |

|     |        | 4.7.1 Selftest Validation Framework                        | 112 |

|     |        | 4.7.2 SGX Runtime Ecosystem Analysis                       | 114 |

|     | 4.8    | Discussion                                                 | 119 |

|     | 4.9    | Conclusion                                                 | 120 |

| 5   | Con    | clusion                                                    | 123 |

|     | 5.1    | Summary of Contributions                                   | 124 |

|     | 5.2    | Future Work                                                | 125 |

|     | 5.3    | Concluding Remarks                                         | 129 |

| Α   | Add    | litional Resources for AION                                | 131 |

|     | A.1    | V                                                          | 131 |

|     | A.2    | Case Study Source Code in C                                | 132 |

| В   | Add    | litional Resources for Faulty Point Unit Attacks           | 137 |

|     | B.1    | Proof-of-concept Enclave Code                              | 137 |

|     | B.2    | Search Algorithm Based on Overflow Exceptions              | 138 |

| С   |        | litional Resources for Pandora                             | 141 |

|     | C.1    | Pandora CLI and Report Generation $(G4) \dots \dots \dots$ | 141 |

|     | C.2    | Static Analysis of Enclave Runtimes                        | 142 |

|     | C.3    | Pandora Breakpoints                                        | 143 |

|     | C.4    | Vulnerability Details                                      | 144 |

| Bi  | bliog  | raphy                                                      | 147 |

| Cı  | ırricu | lum Vitae                                                  | 163 |

| Lis | st of  | Publications                                               | 165 |

|     |        |                                                            |     |

# **List of Figures**

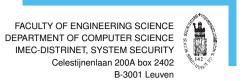

| 1.1   | Overview of confidential computing architecture paradigms | 4  |

|-------|-----------------------------------------------------------|----|

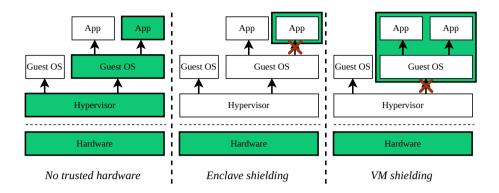

| 1.2   | Enclave architecture call hierarchy                       | 6  |

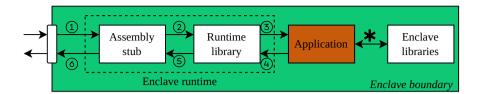

| 1.3   | Intel SGX shielding runtime ecosystem                     | 9  |

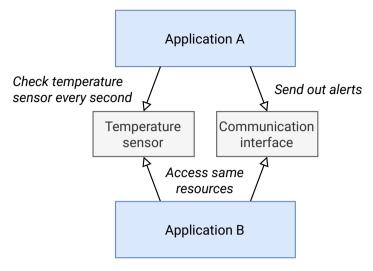

| 2.1   | Aion use case example                                     | 25 |

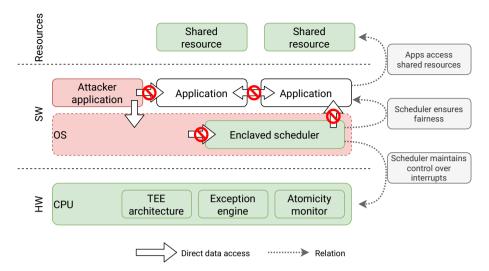

| 2.2   | Aion system overview                                      | 28 |

| 2.3   | Exception engine overview of AION                         | 31 |

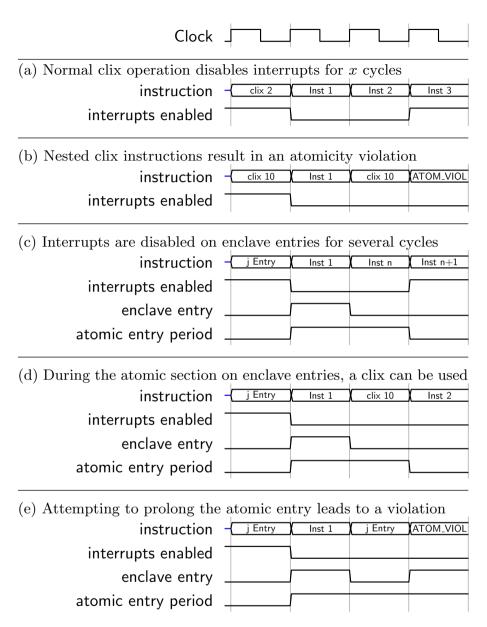

| 2.4   | clix behaviour in AION                                    | 34 |

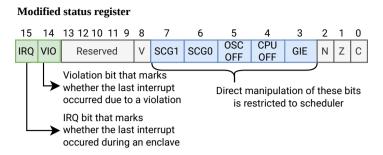

| 2.5   | Aion modifications to the status register                 | 39 |

| 3.1   | Intel SGX enclave model overview                          | 55 |

| 3.2   | Layout of the x87 FPU control word                        | 60 |

| 3.3   | Layout of the MXCSR control/status register               | 61 |

| 3.4   | Histogram of error for secret recovery                    | 75 |

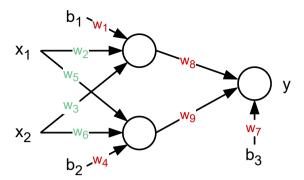

| 3.5   | Structure of the AND network                              | 76 |

| 3.6   | MLaaS system model with enclaves                          | 79 |

| 3.7   | Blender benchmark in SPEC CPU 2017 under attack           | 84 |

| 3.8   | Povray benchmark in SPEC CPU 2017 under attack            | 85 |

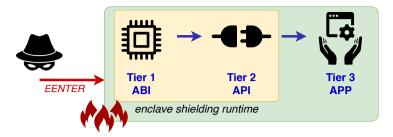

| 4.1   | Enclave shielding runtime overview                        | 94 |

| 4.2   | Overview of the Pandora architecture                      | 99 |

| A.1   | AION atomicity state machine                              | 32 |

| C.1   | Example of an HTML report generated by Pandora            | 45 |

| $C_2$ | Command line interface of Pandora                         | 46 |

# **List of Tables**

|         | AION scheduler overhead                              |            |

|---------|------------------------------------------------------|------------|

| 2.2     | AION activation latencies                            | .5         |

| 3.1     | Proof-of-concept attack executed inside an enclave 6 | <b>i</b> 8 |

| 3.2     | Affected runtimes by the FPU attacks                 | 71         |

|         | MNIST predictions under attack                       |            |

| 3.4     | SPEC CPU 2017 benchmarks                             | 33         |

| 4.1     | Comparison of symbolic-execution tools for SGX       | )7         |

| 4.2     | Overview of Pandora results                          | .3         |

| C.1     | List of breakpoints added by Pandora                 | 13         |

| $C_{2}$ | Detailed overview of Pandora results 14              | LΔ         |

# **List of Abbreviations**

**ABI** application binary interface

**API** application programming interface

AVX advanced vector extensions

**CCA** confidential compute architecture

CI continuous integration

CLI command line interface

CPU central processing unit

${f CVE}$  common vulnerabilities and exposure

**DRPW** device register partial write

**EDL** enclave definition language

EDP enclave development platform

**ELF** executable and linkable format

${f EPC}$  enclave page cache

FPU floating-point unit

**GOT** global offset table

**GPU** graphics processing unit

**ISA** instruction set architecture

libOS library operating system

MCDT MXCSR configuration-dependent timing

MMIO memory-mapped I/O

**OS** operating system

SBDR shared buffers data read SDK software development kit

SECS SGX enclave control structure

SEV Secure Encrypted Virtualization

SGX Software Guard Extensions

**SIMD** single instruction multiple data

SSA state save area

**SSE** Streaming SIMD Extensions

TCB trusted computing base

TCS thread control structure

TDX Trust Domain Extensions

TEE trusted execution environment

TOCTOU time-of-check time-of-use

TPM trusted platform module

VM virtual machine

# Chapter 1

# Introduction

With an ever-decreasing cost of computation resources comes an ever-increasing number of opportunities these resources present. Where devices like the oftcited and highly specialized Apollo guidance computer were unique at their time, devices of similar capabilities have nowadays become commonplace. On the other end of the computing spectrum, highly capable server hardware has become ubiquitous and enables extensive computations on a large scale. Across this spectrum, modern computing architectures are defined by two fundamental characteristics: connectivity to a network of other devices and the increased sharing of devices between potentially heterogeneous stakeholders. Both aspects significantly impact the security of underlying systems. Networking and potentially even global access to a system make any vulnerability an immediate and possibly global threat to a large number of affected systems. Similarly, sharing a platform between potentially unaffiliated stakeholders threatens the confidentiality and integrity of computations if the users are not adequately isolated from each other. In embedded computing, such as safety-critical applications, availability is often an additional concern, and global networking or sharing resources with unknown parties is thus rarely implemented to limit the system's exposure to possible attacks.

Many approaches exist to shield secrets from the impacts of arbitrary network attackers or harmful stakeholders on the same platform. Cryptography allows secret communication between software components over an untrusted network. This is also known as protecting data in transit, and cryptography has established itself as the de-facto standard in modern Internet communication. Encryption is furthermore a powerful paradigm to address the issue of protecting against stakeholders that may access archived data, also called protection of data at

2 \_\_\_\_\_\_ INTRODUCTION

rest. However, to protect data that needs to be accessed, also called protection of data in use, established encryption algorithms are insufficient as they require decryption prior to computation on encrypted data. To address this, multiparty computation [133] and homomorphic encryption [1] are two active areas of research. An orthogonal approach to pure cryptography is to modify the underlying hardware to isolate to-be-protected code from the potentially harmful environment. While these approaches often still utilize cryptographic primitives to protect communication and data at rest, their benefit is that data in use must not be encrypted since the computing party has exclusive access to it. Theoretically, this requires little to no computational overhead to operate on data in use as the overhead is spent in terms of additional hardware to access the data and not during runtime.

In the trajectory of this Ph.D., we focused on the area that is nowadays known as confidential computing, or trusted execution environments (TEEs). TEEs are a type of hardware primitive that isolates software components from the surrounding system [38, 122]. Other hardware approaches with similar or overlapping goals include trusted platform modules (TPMs) [148], virtualization isolation, capability architectures [172], and CPU privilege levels.

This dissertation makes contributions on two fronts. First, we address the gap of applying TEE architectures in safety-critical systems. Our work AION, for the first time, enables availability on the class of embedded enclave architectures, prototyped on the research architecture Sancus [106]. Second, we address the growing complexity of server TEE architectures such as the x86-based Intel Software Guard Extensions (SGX) [11, 98] and the need for proper sanitization when entering and computing in those complex isolation environments. In this part, we first show that floating-point accelerators can be prone to fault-injection attacks via their status and control registers if not properly sanitized on enclave entry. As a follow-up, our contribution Pandora combines insights from this earlier work and related work. With Pandora, we can automatically analyze enclaves from the first instruction to detect a range of vulnerability classes.

# 1.1 Confidential Computing

TEEs are hardware extensions to processor architectures that allow software to shield a region in memory from unwanted access [38]. In doing so, hardware-based TEEs that we consider in this dissertation place their root of trust in exactly these instruction set architecture (ISA) changes. The trusted computing base (TCB) of the resulting shielded environment is thus only the hardware and its associated microcode, as well as the shielded environment itself [122].

This is a drastic reduction to the TCB in the absence of a TEE where the complete software stack that an application is running on has to be trusted. Figure 1.1 illustrates the different levels of encapsulation that modern TEEs provide. Without trusted hardware on the left of the figure, an application receives only protection guarantees resulting from virtual memory management and can, for example, be accessed by the underlying guest operating system (OS) which in turn can itself be accessed by the underlying hypervisor. The only protection with virtual memory comes from the underlying layer creating virtual address spaces that prevent parallel entities on the same level from accessing an entity's data. For a guest OS, this means that the hypervisor is trusted to set up this protection properly, and for an application, the guest OS is trusted to shield an application from other applications running on the same system. In this case, the TCB is quite large, as any module in the aforementioned stack has to be trusted not to leak secrets or impact the application's integrity. The promise of trusted execution is to disrupt this stacked layering of trust. Confidential computing and specifically TEEs present two alternative models of layering: enclave shielding and virtual machine (VM) shielding [38]. In enclave shielding, the application itself is isolated from the surrounding environment, such as the guest OS and other applications. To keep the TCB of an enclaved application minimal, a legacy application can be split up into an untrusted and an enclaved application, and communication between the two can be set up to provide only security-critical services from inside the enclave. Essentially, however, the TCB of the small enclave application only consists of itself and the associated code inside the trusted environment, and the second, untrusted, part of the application must be seen as potentially compromised. To address the complexity of splitting applications into a trusted and an untrusted part, VM shielding draws a larger isolation boundary and also includes the guest OS itself and co-located applications from the underlying hypervisor. This widens the TCB but has the benefit of easing the applicability of this approach since developers can seamlessly adopt many legacy applications into such a VM-based TEE environment.

The choice between both approaches lies in the size of the TCB versus the usability and direct applicability of established and legacy code in the isolation environment. Enclave architectures may suffer in their usability from the small TCB as dynamic libraries may not be usable as the guest OS is untrusted. Similarly, enclaves cannot execute system calls directly from within the enclave. They must either execute system calls via the untrusted application or substitute them for secure versions from within the enclave. VM architectures may accommodate this limitation at the cost of a larger TCB and associated higher computational overhead per isolated application.

While the specific guarantees by a TEE are not clearly defined across the

4 \_\_\_\_\_\_INTRODUCTION

Figure 1.1: Overview of confidential computing architecture paradigms. Green boxes (bold frame) denote the trusted computing base of an application. Trusted hardware prevents access from the guest OS to the application or from the hypervisor to the guest OS, respectively.

ecosystem, the following properties are relevant in the context of this dissertation and can also be seen as the core parts of confidential computing [37]:

Data confidentiality and integrity: Software running inside the isolated environment can protect the confidentiality and integrity of data and ensure that access to the protected data is restricted to the TCB of the isolated software and that untrusted sources cannot tamper this data.

Code integrity: The untrusted environment cannot modify the code executing inside the isolated environment. While the untrusted environment may be able to trigger interrupts that disrupt the execution, all switches into the isolated environment are restricted to predefined entry points.

Attestability: The state of the software loaded in the isolated environment can be proven and reported to an outside stakeholder who can use this proof to establish trust into and create a secure communication channel with the software running in the TEE.

Additional orthogonal properties may be common across multiple TEEs and be useful for certain applications. Such additional properties include confidentiality of isolated code, recoverability from flaws in the underlying hardware, authentication of isolation environments prior to their launch, or direct access to memory-mapped I/O (MMIO) devices from within the isolated environment [37]. We will introduce additional concepts where necessary and when other properties are relevant to the research described in this dissertation.

This dissertation exclusively focuses on the group of enclave architectures. Where relevant, we draw parallels to and reflect insights onto other VM-based architectures such as ARM confidential compute architecture (CCA) [15], Intel Trust Domain Extensions (TDX) [71], AMD Secure Encrypted Virtualization (SEV) [9], and Keystone [86]. In this dissertation, we investigate state-of-the-art, off-the-shelf enclave architectures such as Intel SGX and explore new hardware-software co-designs on research prototype architectures. In the following, we first give an overview of the intricacies of enclave architectures and then introduce the two TEEs that are relevant in this dissertation: Sancus [106] and Intel SGX [40]. Sancus is used as the underlying architecture for the first contribution presented in Chapter 2, and Intel SGX is the underlying architecture for the second and third contribution presented in Chapter 3 and 4.

## 1.1.1 Enclave Architectures

The work presented in this dissertation primarily centers around enclave architectures. These architectures have two core benefits over the VM-based approach: they require a simpler architecture and no virtualization support and thus also apply to light-weight embedded platforms, and they allow to keep the TCB minimal versus VM-based TEEs where the isolation spans a complete guest OS. However, a downside of enclave architectures usually stems from the same lack of a trusted OS in the sense that all code has to statically be included in the loaded enclave instead of dynamically accessing libraries from a shared page set up by the OS. This complicates the compilation process, bloats up enclaves as multiple enclaves cannot share the same virtual memory pages with shared libraries, and complicates the development as developers have to ensure that all functionality is included within the single binary. Similarly, system calls within enclaves require a potentially costly switch from the enclave to the untrusted OS. Any such switch endangers an enclave's security properties and must be handled carefully to neither leak secrets nor rely on potentially harmful information when returning. Both issues may increase development complexity for enclave applications as legacy applications have to be either rewritten for this new paradigm or encapsulated into an enclave runtime that can transparently provide secure versions of system calls and library accesses.

**Enclave Call Hierarchy** To reduce the exposure of an enclave to attacks, all TEEs discussed in the following only support access by jumping to a single pre-defined entry point in the enclave boundary. From this single entry point, the enclave then multiplexes calls to its enclave functions while allowing the developers to carefully design and potentially verify the security of the entry point code. Figure 1.2 illustrates the common call hierarchy from the point of

6 \_\_\_\_\_\_ INTRODUCTION

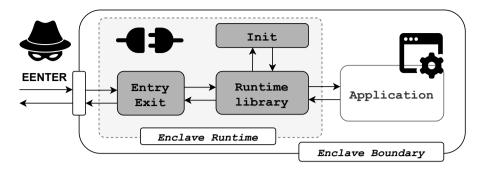

Figure 1.2: Call hierarchy in enclave architectures. On enclave entry,  $\widehat{\ 1}$  an assembly stub sanitizes inputs and  $\widehat{\ 2}$  passes execution to the runtime, which  $\widehat{\ 3}$  calls the application. Application executions may perform  $\widehat{\ *}$  multiple calls to enclave libraries and  $\widehat{\ 4}$  –  $\widehat{\ 6}$  either complete an ecall by returning the call via the runtime and the assembly stub or perform an ocall to the untrusted world.

entering into the single entry point of the enclave to the return to the untrusted world, usually in the form of the untrusted part of an enclaved application. As a common first step, a small section of code, usually programmed in assembly, sanitizes the potentially malicious register state. This section of the program is also known as the application binary interface (ABI) sanitization and also includes a setup of an in-enclave stack and preparing the register state for the switch to code written in higher-level programming languages. The expectation of compilers for higher-level programming languages is usually that the ABI adheres to specific guidelines, such as the System-V ABI [93]. One important task of the ABI assembly stub in enclaves is thus to prepare the ABI and set up the configuration and interface for the compiler-expected state. Depending on whether an enclave runtime is used or not, a dedicated runtime library may serve as a middle point between the ABI sanitization and the enclave application. This runtime library may take over parts of the sanitization of the application programming interface (API), e.g., sanitization of passed pointers. Finally, the runtime library switches to the enclave application, which may make arbitrarily many calls to statically linked libraries within the enclave boundary. Whenever this application enclave has finished its computation, the call is usually returned via the runtime library and the assembly stub to sanitize the ABI and API state, this time to scrub it from secrets that may leak to the untrusted OS.

## 1.1.2 **Sancus**

On the lower end of the computing spectrum, lightweight processor architectures such as the Texas Instruments MSP430 have a 16-bit architecture, run at clock speeds of  $1-20\,\mathrm{MHz}$  and lack many extended processor features that have become

commonplace in modern, more complex processor designs. The core benefits of these processor families are the very low costs per chip and the very low power consumption, combined with the fact that not every application requires extensive computational capabilities. Sancus [106] is an open-source openhardware research prototype TEE that is built on top of such a lightweight architecture, specifically the openMSP430 core by Olivier Girard. The main contribution of Sancus is that it brings an enclave architecture to the lowlevel openMSP430 processor that before supported neither hardware isolation mechanisms nor even a cryptographic coprocessor. Data confidentiality and integrity are achieved with a program counter-based access control that only grants read or write access to a protected region if the current execution is within this region. Code integrity is achieved by limiting switches to the enclave to the first address in the enclave address range and preventing any jumps into the middle of a protected region. The above guarantees allow multiple mutually distrusting enclaves to coexist on the same device without compromising their confidentiality or integrity. To enable secure communication between enclaves, the Sancus design allows enclaves to directly call other enclaves and retrieve the identifier of a caller enclave. Remote attestation with external stakeholders is secured with symmetric keys that are deterministically derived based on device identity and the initial hash of the protected region. Lastly, Sancus, as a hardware-software co-design, also provides compiler modifications to LLVM [92] that allow developers to initialize, program, and interact with enclaves conveniently.

While the Sancus architecture is in many ways simpler than higher-level architectures like Intel SGX, its simplicity allows for a range of features that do not exist on these more complex architectures: secure access to MMIO peripherals from within an enclave, enclaves as interrupt handlers, and driver enclaves that can expose peripherals to other enclaves or untrusted tasks.

Sancus has served as the basis for a range of applications and extensions, such as partial exploratory support for interruptible enclaves [156, 158], side-channel resistant compilers [25, 170], automotive applications [155, 162, 169], and smart home applications [103].

## 1.1.3 Intel SGX

Intel SGX is an enclave architecture that, as of 2023, has been available on processors of the Core-i series from 2015 (generation "Skylake") to 2020 (generation "Comet Lake") as well as on server processors since 2015 [72].

<sup>1</sup>https://opencores.org/projects/openmsp430

8 \_\_\_\_\_\_ INTRODUCTION

In contrast to MSP430, x86 uses a more complex memory architecture based on virtual address spaces. Instead of the program counter-based access protection used in Sancus, Intel SGX uses an enclave page cache (EPC) map that tracks the assignment of virtual pages to enclaves. Since the underlying operating system is seen as fully untrusted but still manages the memory allocation, the assigned EPC pages are protected on enclave creation when the enclave is loaded and the pages are added to the enclave address range (called the ELRANGE) [40]. Upon finalization of the enclave's initialization, an enclave-specific value called the MRENCLAVE value is calculated from all initial enclave pages. In cooperation with some architectural enclaves, this MRENCLAVE value can be used in remote attestation to authenticate the enclave to remote parties and establish a secure channel with remote stakeholders or other enclaves. Importantly, however, this MRENCLAVE value also requires that all initializations of the same enclave result in the same hash, independently of where the enclave has been loaded in the virtual address space [11]. This requires additional complexity within the enclave as common software relocation mechanisms and position-independent code must be initialized within the enclave instead of untrusted software being able to reposition code after loading it into memory.

Once an enclave has been initialized, it can only be entered via special instructions that jump to a predefined enclave entry [98]. This enclave entry is usually written in assembly and follows the same principles as described above in Section 1.1.1. Aside from these ecalls into the enclave, Intel SGX also defines ocalls as the reverse operation where an enclave calls a function outside the enclave that then returns to the enclave. Additional complexity is added by special in-enclave structures such as the SGX enclave control structure (SECS) and thread control structure (TCS) pages that contain important architectural enclave information and local enclave thread information, respectively.

## **Enclave Shielding Runtimes**

Several shielding runtimes have been developed for Intel SGX and have become the de-facto standard for developing enclave applications. These shielding runtimes provide multiple benefits to an application developer: they govern the switches between untrusted and trusted world for ecalls and ocalls; they administer the relocation of position-independent code inside the enclave as part of an initialization step; they provide crucial functions that ease the programming of applications inside the enclave, like functions to check whether a pointer lies inside or outside the enclave; and they often provide an interface to marshall and securely copy data structures into and out of the enclave. Figure 1.3 illustrates the landscape of Intel SGX applications and a part of the ecosystem of these shielding runtimes that has developed as of 2023. While

Figure 1.3: Intel SGX shielding runtime ecosystem of production-ready projects. Most projects depend on only a few root projects ( $\bigstar$ ) that provide core enclave functionality.

many applications are based on the Intel SGX software development kit (SDK), a growing number of projects are based on other shielding runtimes such as Open Enclave [101] or Gramine [144]. Notably, only a few root-level projects exist that serve as the basis TCB for many other projects. All highlighted projects in the figure provide entry-level assembly code that sanitizes the potentially malicious input from the untrusted environment and also provides developers with the functionality to either transparently or actively interact with the untrusted environment securely.

10 \_\_\_\_\_\_INTRODUCTION

## 1.2 Dissertation Motivation and Contributions

In light of this background, we present the three core contributions of this dissertation: Chapter 2 extends the protection guarantees of existing embedded TEEs and Chapter 3 and 4 uncover and automatically detect interface sanitization issues in Intel SGX.

## 1.2.1 Availability Guarantees for Enclaves

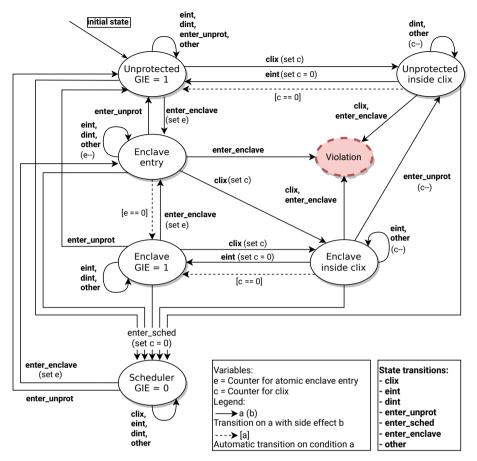

As a first contribution, Chapter 2 presents AION, a hardware-software co-design that can ensure the availability of multiple mutually distrusting parties at the same time. While Sancus can provide strong confidentiality and integrity guarantees to mutually distrusting enclaves, similar to many other TEE architectures, it does not guarantee the availability of any of its protected regions. Specifically, any enclave protected on a Sancus system can be ensured that its confidentiality is protected at all times and that when it executes, its code integrity is protected as well. However, other enclaves or even untrusted code can impact the availability of enclaves by either never scheduling the enclave or triggering interrupts to occur when the enclave is executing. This inevitably results in attackers being able to disrupt deadlines that enclaves may need to meet in a mixed-criticality or even safety-critical system.

Enclave architectures already provide strong security guarantees and are ideal for protecting multiple stakeholders at once that execute their code on a mixedcriticality platform. To additionally guarantee availability, we designed AION as an extension to enclave architectures. At its core, AION moves the real-time scheduler of the system into an enclave. This ensures that the scheduler is protected from outside influences and has the additional benefit that other enclaves do not need to trust the scheduler enclave for confidentiality and integrity since the security protections by the TEE also apply across enclaves. If these other enclaves are willing to trust the scheduler enclave for availability, however, they can request to experience periodic scheduling or similar scheduling guarantees as needed. The scheduler enclave then serves as a small TCB for availability only and must ensure that it only approves scheduling guarantees when they are possible even in a worst-case scenario. To provide hard guarantees on the upper bound of this worst-case scenario, we additionally equip AION with a concept of bounded atomicity. Only the scheduler enclave is in full control of interruptability and can disable interrupts. All other enclaves and untrusted software on the system only have access to a special clix instruction that disables interrupts for a bounded number of cycles. A specially designed availability monitor and an exception engine for enclaves ensure the correct

handling of all edge cases in hardware. With this hardware-software co-design, AION can provide hard real-time guarantees to multiple stakeholders at once, allowing system designers and developers to specifically design their real-time applications with strong confidentiality, integrity, and availability protections.

Our work, for the first time, combines lightweight embedded TEEs with mixed-criticality systems requiring strong hard real-time guarantees. While architectures like ARM TrustZone have existed for multiple years and are starting to be applied in embedded applications that require availability guarantees, AION demonstrates that availability protections are also possible without placing the scheduler into the TCB for confidentiality and integrity. Since ARM TrustZone is similar to the VM-based model explained above, this nuanced trust relationship is not possible, as the scheduler and the complete guest OS are fully trusted by the protected applications. AION furthermore demonstrates that even the architecture class below classical TrustZone devices, *i.e.*, the architecture class of 16-bit processors, can benefit from TEE capabilities with strong availability guarantees.

#### Publication data:

F. Alder, J. Van Bulck, F. Piessens, and J. T. Mühlberg. "Aion: Enabling Open Systems through Strong Availability Guarantees for Enclaves". In: *Proceedings of the 28th ACM Conference on Computer and Communications Security (CCS'21)*. ACM, 2021, pp. 1357–1372

## 1.2.2 Interface Sanitization in Intel SGX

The second part of this dissertation is concerned with the interface between the untrusted world and Intel SGX enclaves.

As a first contribution in this part, we show in Chapter 3 that former register sanitization in Intel SGX shielding runtimes was insufficient. Specifically, most shielding runtimes omitted to set configuration and control registers of the x87 floating-point unit (FPU) and of the Streaming SIMD Extensions (SSE) to a safe value upon entering the enclave. At the time of investigation, all seven investigated shielding runtimes were vulnerable to at least some form of FPU register attack. Our work shows that even seemingly minor control registers can have potentially grave impacts due to the strong integrity protection promises of Intel SGX. We highlight this with three case studies and illustrate that unexpected floating point precision and rounding modes can majorly impact the resulting quality of generated output. These attacks are non-trivial to mitigate and show that exception masks can even leak enclave secrets in some cases.

12 \_\_\_\_\_\_INTRODUCTION

This contribution does not stand alone in showing that the interface between untrusted world and Intel SGX enclaves must be properly sanitized. Van Bulck et al., for example, showed in 2019 that all enclave interaction on both ABI and API can be problematic if not handled carefully [157]. At the same time, several of the investigated shielding runtimes are of high quality and investment by the respective vendors, and the functions and assembly stubs that perform sanitizations can be seen as having received extensive care from their developers. For example, our study of shielding runtimes from 2022 showed that it is common for these shielding runtimes to have changed as many lines of code in the assembly stubs of up to two times their actual size since the project began [153]. Yet, issues on both the ABI and API levels keep reoccurring, as happened in early 2023, for example, when Intel provided new recommendations of SSE configuration values that refine the earlier recommendations that were also applied as a response to our attacks [73].

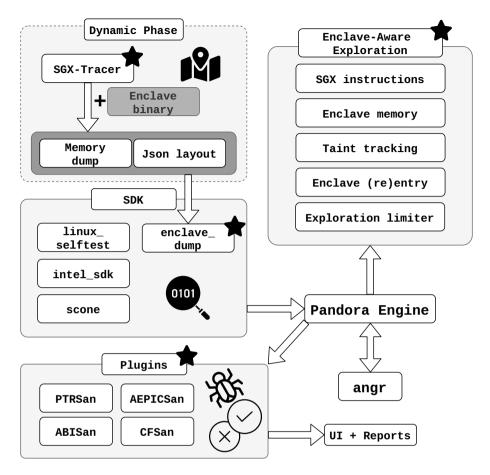

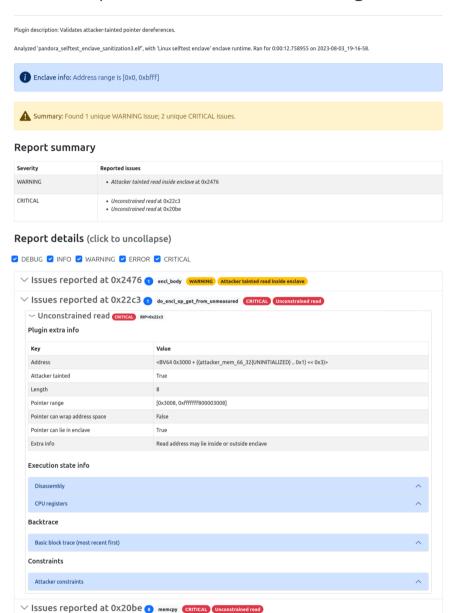

As a second contribution in this part, and this dissertation's third and final contribution, we thus present a framework in Chapter 4 that allows symbolic execution of Intel SGX enclaves and finding known classes of interface vulnerabilities, such as the ones reported in our earlier contribution. This framework, called Pandora, brings several innovations to, for the first time, allow principled and truthful symbolic execution of enclave binaries. Pandora uses a novel initial phase to dump the full enclave memory at enclave creation time and uses this dump to truthfully simulate enclave execution beginning at the first assembly instruction. Prior work has already attempted and partially succeeded in symbolically executing Intel SGX enclaves but has focussed on the applications instead of the crucial but vulnerable shielding runtimes. Our work, for the first time, takes care to fully encompass all functionality provided by these enclave shielding runtimes without skipping or simulating essential functionality. In addition, Pandora is written in a modular approach and can utilize the analyses provided by the underlying symbolic execution engine angr and pass information on to a new system of powerful plugins that can flexibly be enabled on demand. These plugins extend the capabilities of angr and perform the actual vulnerability detection and reporting. We use Pandora to find seventeen new vulnerabilities across eight partially closed-source shielding runtimes.

#### Publication data:

F. Alder, J. Van Bulck, D. Oswald, and F. Piessens. "Faulty Point Unit: ABI poisoning attacks on Intel SGX". in: *Annual Computer Security Applications Conference (ACSAC)*. 2020, pp. 415–427

F. Alder, L.-A. Daniel, D. Oswald, F. Piessens, and J. Van Bulck. "Pandora: Principled Symbolic Validation of Intel SGX Enclave Runtimes". In:  $In\ submission.\ 2023$

## 1.2.3 Open Science and Ethical Considerations

All software vulnerabilities discussed in this work have been reported to the respective vendors, and where possible, we have supported the vendors in validating the applied mitigations. Overall, the work in this Ph.D. trajectory has directly or indirectly led to the finding of 211 vulnerability instances, the assignment of twelve common vulnerabilities and exposures (CVEs), and software patches across nine projects. In several instances, our active engagement with the open-source maintainers has led to more refined patches, thus improving end-user security in the emerging Intel SGX software ecosystem. Furthermore, all research performed during this dissertation has been open-sourced. For the three core contributions of this dissertation, the details are:

AION: Enabling Open Systems through Strong Availability Guarantees for Enclaves The Sancus hardware and compiler infrastructure changes have been included in the Sancus core architecture on GitHub.<sup>2</sup> All software modifications to the Riot OS [17] were published as open source in their own repository under the same Sancus organization<sup>3</sup>, and a Docker container with the AION architecture is automatically built and provided on GitHub.

Faulty Point Unit: ABI Poisoning Attacks on Intel SGX During the course of this contribution, we found and responsibly disclosed six vulnerabilities across six runtimes, one of which is a runtime on the RISC-V architecture, leading to the assignment of two CVEs. The artifact and corresponding Docker container of this contribution are fully available on GitHub<sup>4</sup> and continuous integration regularly verifies its reproducibility up to this date. As part of the ACSAC conference, the artifact received the highest ACM rating of "Artifacts Evaluated - Reusable v1.1", and the paper subsequently received a "distinguished paper with artifacts" award.

<sup>&</sup>lt;sup>2</sup>https://github.com/sancus-tee

<sup>3</sup>https://github.com/sancus-tee/sancus-riot

<sup>4</sup>https://github.com/fritzalder/faulty-point-unit

14 \_\_\_\_\_\_INTRODUCTION

Pandora: Principled Symbolic Execution of Intel SGX Enclaves At this time, Pandora is in submission. During working on this project, we found 174 new vulnerability instances across 10 runtimes, leading to the assignment of 7 CVEs. Once this submission concludes, Pandora will be released as open-source, together with extensive documentation to support its use during the development processes of enclave software<sup>5</sup>.

## 1.3 Other Contributions

In parallel to the three major contributions outlined in this dissertation, I authored or contributed to several additional publications that are summarized as follows.

Efficient and Timely Revocation of V2X Credential In vehicle-to-everything communication, vehicles are expected to communicate with an abundance of other vehicles and communication parties alongside the road. To ensure the security and safety of all involved participants, malicious or misbehaving parties must be punishable in a timely manner, e.g., via revocation of their credentials or pseudonyms. This paper presents a mechanism for self-revocation of vehicle pseudonymous credentials based on a TEE inside each vehicle. The presented mechanism is formally verified with the Tamarin prover and can provide a predictable upper bound on revocation time based on configurable parameters. In addition to the formal verification, the paper presents a statistical model of the expected size of the revocation list of each network participant, and a simulation to showcase its feasibility even for larger networks.

Gianluca Scopelliti is the main author of this work and developed the core design together with Christoph Baumann. I contributed with discussions on the design and the statistical model of the certificate revocation list as well as writing of the concerned chapters.

G. Scopelliti, C. Baumann, F. Alder, E. Truyen, and J. T. Mühlberg. "Efficient and Timely Revocation of V2X Credentials". In: 31st Annual Network and Distributed System Security Symposium (NDSS'24). The Internet Society, 2024

<sup>&</sup>lt;sup>5</sup>https://github.com/pandora-tee

About Time: On the Challenges of Temporal Guarantees in Untrusted Environments This paper investigates how time can be accessed by enclaves from within a TEE and classifies five levels of this access: no access to trusted time; checking the monotonicity of untrusted time; access to an external trusted time source; access to the trusted time source with a known delay; and lastly atomic access to the trusted time source. We found that Intel SGX can only provide access to an external trusted time source when using Intel platform services that are not always available. Furthermore, in the future, Intel SGX enclaves may access trusted time atomically if never interrupted. Other TEEs like Intel TDX or Arm CCA have the potential to provide access with a known delay to a trusted time source, albeit most TEEs cannot access time atomically. Our work concludes by enumerating multiple applications of trusted time in TEEs and rating them according to their required trusted time level.

I was the main author of this paper and collaborated with Gianluca Scopelliti and Jo Van Bulck under the supervision of Jan Tobias Mühlberg.

F. Alder, G. Scopelliti, J. Van Bulck, and J. T. Mühlberg. "About Time: On the Challenges of Temporal Guarantees in Untrusted Environments". In: 6th Workshop on System Software for Trusted Execution (SysTEX Workshop). 2023

End-to-End Security for Distributed Event-Driven Enclave Applications on Heterogeneous TEEs Hardware isolation primitives provide strong local assurances that can be attested to outside parties. This paper introduces a framework that links local peripheral input on one device to a decision made on another. With this so-called *authentic* execution, we can guarantee that a decision made on a device has only been made as a response to peripheral input received by a remotely attested device. Conversely, the output would not have been created without adequate input. Our open-source framework supports Sancus, Intel SGX, and ARM TrustZone to allow for heterogeneity, and we showcase it with a case study of a smart home application.

Gianluca Scopelliti is the first author of this paper. I contributed with the mentoring of Gianluca Scopelliti during his master's thesis, contributed to the current designs of the authentic execution framework, and aided in writing the final text.

G. Scopelliti, S. Pouyanrad, J. Noorman, F. Alder, C. Baumann, F. Piessens, and J. T. Mühlberg. "End-to-End Security for Distributed Event-Driven

16 \_\_\_\_\_\_ INTRODUCTION

Enclave Applications on Heterogeneous TEEs". In: ACM Transactions on Privacy and Security (TOPS) (Apr. 2023)

A Case for Unified ABI Shielding in Intel SGX Runtime As a result of our investigation of FPU sanitization in Intel SGX and the earlier work on Intel SGX interface sanitization [157], this paper makes a case against the heterogeneous landscape of enclave assembly code. Since most enclave shielding runtimes need to perform the same register sanitization and need to set up their own secure environment, we argue that unification of the small code base that performs this task is necessary. Some intricacies would be necessary to allow for a diverse set of environments and programming languages that follow the execution of the unified stub, but a clear benefit would be the starkly reduced patch timelines to mitigate known ABI-level issues.

Jo Van Bulck was the main author of this paper, and we shared work equally under the supervision of Frank Piessens.

J. Van Bulck, F. Alder, and F. Piessens. "A Case for Unified ABI Shielding in Intel SGX Runtimes". In: 5th Workshop on System Software for Trusted Execution (SysTEX Workshop). 2022

Secure End-to-End Sensing in Supply Chains This paper serves as a case study of how to protect complex supply chains by combining trusted hardware and blockchain-backed ledgers. In supply chains, shipments are passed from the producer over multiple shipment providers down to the final customer. A common issue in this environment is trust, as in modern supply chains, stakeholders rarely trust all other stakeholders that preceded it in the order of events. If a shipment arrives with faults, a stakeholder may not always be able to prove that the defect existed when it received the shipment. Similarly, even the absence of faults must be proven, as a disrupted cold chain cannot always be immediately detected. To tackle these issues, our work designs an architecture that relies on embedded TEEs like Sancus to draw a secure, integrity-protected path from the sensor to a blockchain-backed ledger in a cloud environment. With this architecture, stakeholders no longer need to place trust in prior stakeholders but only need to trust the underlying hardware and its integration into the shipping unit.

Jan Pennekamp is the first author of this paper. He, I, Roman Matzutt, and Jan Tobias Mühlberg had equal parts in writing under the supervision of

Frank Piessens and Klaus Wehrle. This paper resulted in a bachelor's thesis at RWTH-Aachen University, which I co-supervised as an external advisor.

J. Pennekamp, F. Alder, R. Matzutt, J. T. Mühlberg, F. Piessens, and K. Wehrle. "Secure End-to-End Sensing in Supply Chains". In: 2020 IEEE Conference on Communications and Network Security (CNS). 2020, pp. 1–6

#### 1.4 Dissertation Outline

The remainder of this dissertation is structured as follows. In the first part of our contributions, Chapter 2 presents our work on AION, which brings strong availability guarantees to lightweight enclave architectures. Chapter 3 then begins the second part of our contributions with our attacks on Intel SGX via the FPU configuration registers. To aid developers in this fast-paced landscape of interface vulnerabilities, Chapter 4 continues this second part with our third contribution and presents Pandora that can automatically detect common vulnerabilities in enclave binaries. Chapter 5 then concludes this dissertation and presents opportunities for future work.

Chapter 2 to 4 are based on the previously peer-reviewed publications as marked in the respective chapters and only contain minor modifications to fit the style of this text. A preamble precedes each chapter to place the work in the context of this Ph.D. trajectory and to present related work in the area since publication.

# Chapter 2

# AION: Enabling Open Systems through Strong Availability Guarantees for Enclaves

This chapter was previously published as:

**F. Alder**, J. Van Bulck, F. Piessens, and J. T. Mühlberg. "Aion: Enabling Open Systems through Strong Availability Guarantees for Enclaves". In: *Proceedings of the 28th ACM Conference on Computer and Communications Security (CCS'21)*. ACM, 2021, pp. 1357–1372

#### **Preamble**

This first contribution has been the final result of long-going discussions in our research group on interruptability and availability guarantees on hardware-based trusted execution environments (TEEs). Many of these discussions started before this Ph.D. trajectory began in 2019, as Jo Van Bulck already discussed some weak points of architectures like Sancus when it comes to availability in his master's thesis [152]. A follow-up publication then outlined necessary steps to

take to make Sancus enclave a candidate for real-time applications [156]. Many of the ideas and contributions of that prior work have impacted the design of Aion.

The core issue with TEE architectures like Sancus at the time of publication was that lightweight embedded security architectures prioritized the confidentiality and integrity of a system at the cost of availability. For example, both the original Sancus work [107] as well as the follow-up Sancus 2.0 version [106] were configured to reset the processor when a violation occurs, and this was common in similar architectures like SMART [50] or VRASED [109]. This, however, is a stop-gap approach for any system that is supposed to provide availability, as it gives attackers a convenient opportunity to reset the processor and impact real-time deadlines. Similarly, neither the original Sancus 2.0 work nor any related work at that time like SMART intended enclaves to be interruptible. As a first work, TrustLite [83] explored a hardware-level interrupt engine for enclaves that uses an exception engine to securely store the register state to a secure location before sanitizing it for the untrusted exception handler. Van Bulck et al. [156, 158] implemented an interrupt mechanism to Sancus enclaves that is similar to this earlier work by TrustLite. Busi et al. [29] formally verified a Sancus interrupt handler that was hardened against side channels. An important drawback of these designs is, however, that interruptability requires the cooperation of the enclave, as enclaves are able to completely disable interrupts and stall the system. Orthogonally, Masti et al. [97] presented a means of bounded atomicity in embedded system for scheduling decisions. With AION we refine and combine these multiple directions of research and present a solution to the long-standing development of enclave interruptability and availability guarantees. AION ensures that enclaves can be interrupted without impacting their security but cannot disable interrupts as a means of unboundedly disrupting the availability of the whole system.

After the publication of AION, several works have approached the same issue of availability on the ARM TrustZone architecture. RT-TEE [166] provides the secure world with an event-driven hierarchical scheduler and device drivers for I/O. This allows RT-TEE to guarantee availability even in the case that the normal world is compromised. The authors showcase their prototype on two types of processors and present several case studies showing their approach's feasibility. Furthermore, Van Eyck et al. built MrTEE as a practical framework to build real-time compliant applications with commodity software and hardware without requiring extensive software modifications, as is the case with RT-TEE [161]. As a result of their underlying TrustZone architecture, both essentially differ from the guarantees provided by AION. Where AION only requires enclaves to trust the scheduler for availability only, as confidentiality and integrity are protected by the underlying hardware mechanisms, TrustZone only

provides the security guarantees for the whole secure world. Thus, the scheduler that is executed in the secure world must be fully trusted by the protected applications, both for availability as well as for confidentiality and integrity. The TrustZone approaches are thus different in their isolation granularity from the approaches discussed and presented in this chapter.

With the conference publication, AION contributed an open-source artifact that was integrated into the Sancus project<sup>1</sup>. This integration was not performed as a duplication of the code base of Sancus but was instead embedded into the existing code base. A Sancus core can be configured via pre-compiler directives that define whether a Sancus core is generated with availability capabilities or not. Together with this embedding into the existing core, we also integrated the availability engine into the existing continuous integration pipeline of Sancus and enabled regular testing of the AION hardware functionality, as well as the regular building of Docker containers that can be used as a basis for development with either AION or Sancus. Additionally, as part of this artifact, AION uses a new, faster hardware simulator based on Verilator<sup>2</sup> that can generate cycle-accurate simulations of AION within seconds instead of the prior simulator that required several minutes for the same task. Lastly, AION was the basis for a master's thesis that investigated remaining issues concerning the schedulability of systems built on AION [65].

#### 2.1 Introduction

With the increased connectivity of devices all across the computing spectrum comes an increasing demand for systems that are not locked down but are more dynamic and open to changes after they are deployed in the real world. An *open* system runs software components (tasks, processes, ...) from several stakeholders that do not necessarily trust each other. The resources of such system, including memory, devices, and the CPU, must be shared among these software components without introducing security vulnerabilities that would allow a malicious component to violate the security expectations of another component. Traditionally, Operating System (OS) kernels have the responsibility of enforcing appropriate isolation between components, and, hence, the OS kernel has been part of the Trusted Computing Base (TCB).

However, experience has shown that operating system kernels can have vulnerabilities too, and several approaches have been explored to reduce the amount of trust in the OS kernel:

<sup>1</sup>https://github.com/sancus-tee

<sup>&</sup>lt;sup>2</sup>https://verilator.org/

First, there is a long line of work in reducing the *size* of kernels (e.g., move to microkernels), or relying on simpler hypervisors or security monitors for enforcing isolation [23, 94, 129]. The key idea is that the trusted layer of software gets smaller, but all software components still need to fully trust the system software for any of their security properties.

Second, formal verification of system software has been proposed as a mechanism to reduce the likelihood of vulnerabilities, and, hence, to better justify the level of trust in system software [66, 82].

Third, work in the trusted computing research area has developed the idea of Trusted Execution Environments (TEEs) or enclaves [8, 19, 28, 83, 86, 98, 106]. These approaches make it possible to remove most (if not all) system software from the TCB, but they cannot guarantee all desired security properties. More specifically, while integrity and confidentiality of enclaves can be guaranteed with a TCB consisting of just the enclave software itself and the hardware, no availability guarantees can be provided. More generally, these systems can provide strong guarantees for resources (like memory) that are spatially shared, but not for resources (like CPU time) that are temporally shared. In the best case (for instance, in Intel SGX), the operating system kernel can preempt temporally shared resources from misbehaving enclaves, at the cost of having to trust the kernel for availability properties. In other cases, there are no availability guarantees in the presence of malicious enclaves.

The objective of this paper is to improve the state-of-the-art in this third approach. We propose a hardware/software co-design that supports classic enclave-like isolation of software components in an open system, and that improves on that classic isolation by also providing availability guarantees. Our system supports the secure temporal sharing of resources (including CPU and I/O devices) among mutually distrusting software components with a small TCB. More specifically, a given enclave software component needs to trust: (i) its own code and the hardware for confidentiality and integrity properties, and (ii) its own code, the hardware, the drivers of the shared devices it requires access to, and a small, trusted scheduler enclave for availability properties. Crucially, since the scheduler is only trusted for availability, our design protects the confidentiality and integrity of vital enclave applications even against a misbehaving scheduler. Furthermore, when the scheduler is well-behaved, our design can provide strong availability guarantees (including real-time guarantees) to software components in the presence of arbitrary malicious software on the platform outside the TCB (including malicious enclaves, malicious drivers for devices not used by this specific component, and system software besides the trusted scheduler).

Our design targets small embedded systems (specifically, our prototype is based

on a TI MSP430 16-bit processor running the RIOT OS), both because these can benefit most from availability and real-time guarantees, and because this allows us to focus on the essence of our design: building on preemption combined with a safe bounded atomicity primitive. Extensions to larger systems, such as for instance Intel SGX-scale processors, are not in the scope of this paper, and are left for future work.

In summary, the contributions of this paper are:

- a novel hardware-software co-design of a security architecture for open systems that extends the strong security properties of modern hardware TEEs with strong guarantees on enclave availability, even in the presence of powerful software adversaries on the same platform.

- a prototype implementation built by extending an existing TI MSP430-based TEE and by extending the existing RIOT IoT operating system.

- a case-study driven evaluation of the security and availability provisions and the costs of the design.

# 2.2 Problem and Assumptions

To illustrate the problem and our platform requirements, we first discuss the base platform that we use as a starting point for our work. We then describe a simple application scenario with specific security and availability needs that cannot be realized with classic TEE implementations. Finally we generalize this to derive platform requirements and discuss these in the context of related work.

In general, we aim to support *open* systems, which are systems that allow multiple distrusting stakeholders to dynamically load arbitrary applications at runtime. While it is obviously possible to combine an open system with priority-based scheduling, the interesting and most difficult case is dealing with mutually distrusting stakeholders executing code with the same priority. Only in this case resources have to be divided fairly.

#### 2.2.1 Generalized Base Platform